热门关键词:

概念

I2C 总线支持任何IC 生产过程(NMOS CMOS、双极性)。通过串行数据(SDA)线和串行时钟 SCL)线在连接到总线的器件间传递信息。每个器件都有一个唯一的地址识别(无论是微控制器——MCU、LCD 驱动器、存储器或键盘接口),而且都可以作为一个发送器或接收器(由器件的功能决定)。很明显,LCD 驱动器只能作为接收器,而存储器则既可以接收又可以发送数据。除了发送器和接收器外,器件在执行数据传输时也可以被看作是主机或从机(见表1)。主机是初始化总线的数据传输并产生允许传输的时钟信号 的器件。此时,任何被寻址的器件都被认为是从机。 I2C 总线术语的定义

特征

1、只要求两条总线线路:一条串行数据线SDA,一条串行时钟线SCL;

2、每个连接到总线的器件都可以通过唯一的地址和一直存在的简单的主机/从机关系软件设定地址,主机可以作为主机发送器或主机接收器;

3、它是一个真正的多主机总线,如果两个或更多主机同时初始化,数据传输可以通过冲突检测和仲裁防止数据被破坏;

4、串行的8 位双向数据传输位速率在标准模式下可达100kbit/s,快速模式下可达400kbit/s,高速模式下可达3.4Mbit/s;

5、连接到相同总线的IC 数量只受到总线的最大电容400pF 限制。

术语

发送器:发送数据到总线的器件;

接收器:从总线接收数据的器件;

主机:启动数据传送并产生时钟信号的设备;

从机:被主机寻址的器件;

多主机:同时有多于一个主机尝试控制总线但不破坏传输;

主模式:用I2CNDAT支持自动字节计数的模式;位I2CRM,I2CSTT,I2CSTP控制数据的接收和发送;

从模式:发送和接收操作都是由I2C模块自动控制的;

仲裁:是一个在有多个主机同时尝试控制总线但只允许其中一个控制总线并使传输不被破坏的过程;

同步:两个或多个器件同步时钟信号的过程 。

位传输

由于连接到I2C 总线的器件有不同种类的工艺(CMOS、NMOS、PMOS、双极性),逻辑0(低)和逻辑1(高)的电平不是固定的,它由电源VCC的相关电平决定,每传输一个数据位就产生一个时钟脉冲。

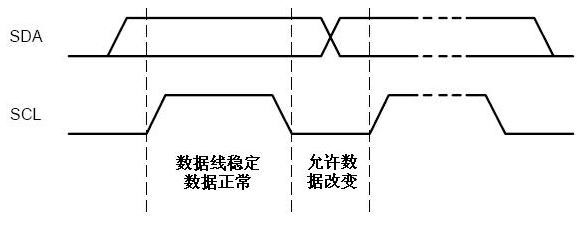

数据有效

在传输数据的时候,SDA线必须在时钟的高电平周期保持稳定,SDA的高或低电平状态只有在SCL 线的时钟信号是低电平时才能改变 。

I2C位传输数据有效性

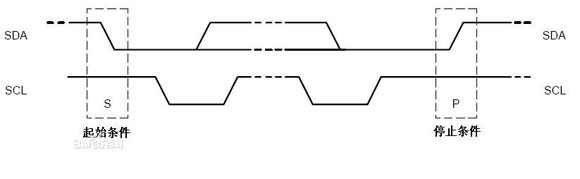

起始停止

SCL 线是高电平时,SDA 线从高电平向低电平切换,这个情况表示起始条件;

SCL 线是高电平时,SDA 线由低电平向高电平切换,这个情况表示停止条件。

起始和停止条件一般由主机产生,总线在起始条件后被认为处于忙的状态,在停止条件的某段时间后总线被认为再次处于空闲状态。

起始和停止条件

如果产生重复起始条件而不产生停止条件,总线会一直处于忙的状态,此时的起始条件(S)和重复起始条件(Sr) 在功能上是一样的。

数据传输

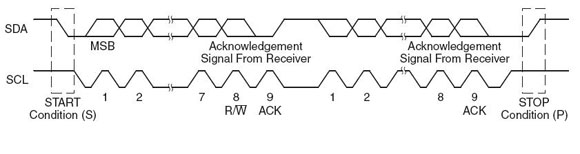

字节格式

发送到SDA 线上的每个字节必须为8 位,每次传输可以发送的字节数量不受限制。每个字节后必须跟一个响应位。首先传输的是数据的最高位(MSB),如果从机要完成一些其他功能后(例如一个内部中断服务程序)才能接收或发送下一个完整的数据字节,可以使时钟线SCL 保持低电平,迫使主机进入等待状态,当从机准备好接收下一个数据字节并释放时钟线SCL 后数据传输继续。

应答响应

数据传输必须带响应,相关的响应时钟脉冲由主机产生。在响应的时钟脉冲期间发送器释放SDA 线(高)。

在响应的时钟脉冲期间,接收器必须将SDA 线拉低,使它在这个时钟脉冲的高电平期间保持稳定的低电平。

通常被寻址的接收器在接收到的每个字节后,除了用CBUS 地址开头的数 据,必须产生一个响应。当从机不能响应从机地址时(例如它正在执行一些实时函数不能接收或发送),从机必须使数据线保持高电平,主机然后产生一个停止条件终止传输或者产生重复起始条件开始新的传输。

I2C总线数据传输和应答

如果从机接收器响应了从机地址,但是在传输了一段时间后不能接收更多数据字节,主机必须再一次终止传输。这个情况用从机在第一个字节后没有产生响应来表示。从机使数据线保持高电平,主机产生一个停止或重复起始条件。

如果传输中有主机接收器,它必须通过在从机不产生时钟的最后一个字节不产生一个响应,向从机发送器通知数据结束。从机发送器必须释放数据线,允许主机产生一个停止或重复起始条件。

时钟同步

所有主机在SCL线上产生它们自己的时钟来传输I2C总线上的报文。数据只在时钟的高电平周期有效,因此需要一个确定的时钟进行逐位仲裁。

时钟同步通过线与连接I2C 接口到SCL 线来执行。这就是说SCL 线的高到低切换会使器件开始数它们的低电平周期,而且一旦器件的时钟变低电平,它会使SCL 线保持这种状态直到到达时钟的高电平。但是如果另一个时钟仍处于低电平周期,这个时钟的低到高切换不会改变SCL 线的状态。因此SCL 线被有最长低电平周期的器件保持低电平。此时低电平周期短的器件会进入高电平的等待状态。

当所有有关的器件数完了它们的低电平周期后,时钟线被释放并变成高电平。之后,器件时钟和SCL线的状态没有差别,而且所有器件会开始数它们的高电平周期。首先完成高电平周期的器件会再次将SCL线拉低。

这样产生的同步SCL 时钟的低电平周期由低电平时钟周期最长的器件决定,而高电平周期由高电平时钟周期最短的器件决定。

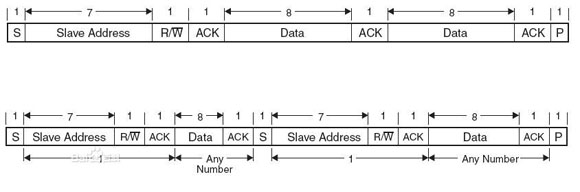

寻址方式

7位

第一个字节的头7 位组成了从机地址,最低位(LSB)是第8 位,它决定了传输的 方向。第一个字节的最低位是“0”,表示主机会写信息到被选中的从机;“1”表示主机会向从机读信息,当发送了一个地址后,系统中的每个器件都在起始条件后将头7 位与它自己的地址比较,如果一样,器件会判定它被主机寻址,至于是从机接收器还是从机发送器,都由R/W 位决定的哦。

普通的和带重复开始条件的7位地址格式

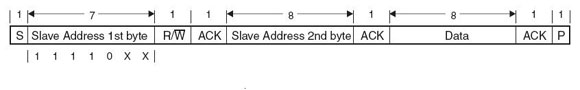

10位

10位寻址和7 位寻址兼容,而且可以结合使用。

10位寻址采用了保留的1111XXX 作为起始条件(S),或重复起始条件(Sr )的后第一个字节的头7 位。

10 位寻址不会影响已有的7 位寻址,有7 位和10 位地址的器件可以连接到相同的I2C 总线。它们都能用于标准模式(F/S)和高速模式(Hs)系统。

I2C总线10位地址格式

保留地址位1111XXX 有8 个组合,但是只有4 个组合11110XX 用于10 位寻址,剩下的4个组合11111XX 保留给后续增强的I2C 总线。

10 位从机地址是由在起始条件(S) 或重复起始条件(Sr )后的头两个字节组成。

第一个字节的头7 位是11110XX 的组合,其中最后两位(XX) 是10 位地址的两个最高位(MSB)。

第一个字节的第8 位是R/W 位,决定了传输的方向,第一个字节的最低位是“0”表示主机将写信息到选中的从机,“1 ”表示主机将向从机读信息。

如果R/W 位是“0 ”,则第二个字节是10 位从机地址剩下的8 位;如果R/W 位是“1” 则下一个字节是从机发送给主机的数据。

快速模式

快速模式器件可以在400kbit/s 下接收和发送。最小要求是:它们可以和400kbit/s 传输同步,可以延长SCL 信号的低电平周期来减慢传输。快速模式器件都向下兼容,可以和标准模式器件在0~100kbit/s 的I2C 总线系统通讯。但是,由于标准模式器件不向上兼容,所以不能在快速模式I2C 总线系统中工作。快速模式I2C 总线规范与标准模式相比有以下额外的特征:

1、最大位速率增加到400kbit/s;

2、调整了串行数据(SDA) 和串行时钟(SCL )信号的时序;

3、快速模式器件的输入有抑制毛刺的功能,SDA 和SCL输入有施密特触发器;

4、快速模式器件的输出缓冲器对SDA 和SCL 信号的下降沿有斜率控制功能;

5、如果快速模式器件的电源电压被关断,SDA 和SCL 的I/O 管脚必须悬空,不能阻塞总线;

6、连接到总线的外部上拉器件必须调整以适应快速模式I2C 总线更短的最大允许上升时间。对于负载最大是200pF 的总线,每条总线的上拉器件可以是一个电阻,对于负载在200pF~400pF 之间的总线,上拉器件可以是一个电流源(最大值3mA )或者是一个开关电阻电路。

高速模式

高速模式(Hs 模式)器件对I2C 总线的传输速度有具大的突破。Hs 模式器件可以在高达3.4Mbit/s 的位速率下传输信息,而且保持完全向下兼容快速模式或标准模式(F/S 模式)器件,它们可以在一个速度混合的总线系统中双向通讯。

Hs 模式传输除了不执行仲裁和时钟同步外,与F/S 模式系统有相同的串行总线协议和数据格式。

高速模式下I2C 总线规范如下:

1、Hs 模式主机器件有一个SDAH 信号的开漏输出缓冲器和一个在SCLH 输出的开漏极下拉和电流源上拉电路。这个电流源电路缩短了SCLH 信号的上升时间,任何时候在Hs 模式,只有一个主机的电流源有效;

2、在多主机系统的Hs 模式中,不执行仲裁和时钟同步,以加速位处理能力。仲裁过程一般在前面用F/S 模式传输主机码后结束;

3、Hs 模式主机器件以高电平和低电平是1:2 的比率产生一个串行时钟信号。解除了建立和保持时间的时序要求;

4、可以选择Hs 模式器件有内建的电桥。在Hs 模式传输中,Hs 模式器件的高速数据(SDAH)和高速串行时钟(SCLH )线通过这个电桥与F/S 模式器件的SDA 和SCL 线分隔开来。减轻了SDAH 和SCLH 线的电容负载,使上升和下降时间更快;

5、Hs 模式从机器件与F/S 从机器件的唯一差别是它们工作的速度。Hs 模式从机在SCLH 和SDAH输出有开漏输出的缓冲器。SCLH 管脚可选的下拉晶体管可以用于拉长SCLH 信号的低电平,但只允许在Hs 模式传输的响应位后进行;

6、Hs 模式器件的输出可以抑制毛刺,而且SDAH 和SCLH 输出有一个施密特触发器;

7、Hs 模式器件的输出缓冲器对SDAH 和SCLH 信号的下降沿有斜率控制功能。

常用念法

I2C(Inter-Integrated Circuit)是内部整合电路的称呼,是一种串行通讯总线,使用多主从架构,由飞利浦公司在1980年代为了让主板、嵌入式系统或手机用以连接低速周边装置而发展。I2C的正确读法为"I-squared-C" ,而"I-two-C"则是另一种错误但被广泛使用的读法,在中国则多以"I方C"称之。

在Wikipedia中的解释也有“I-two-C”的说法:I2C (Inter-Integrated Circuit, referred to as I-squared-C, I-two-C, or IIC)