内部结构

AT89C2051是一个带有2K字节闪速可编程可擦除只读存储器(EEPROM)的低电压,高性能8位CMOS微处理器。它采用ATMEL的高密非易失存储技术制造并和工业标准MCS-51指令集和引脚结构兼容。通过在单块芯片上组合通用的CPLI和闪速存储器,ATMEL的AT89C2051是一强劲的微型处理器,它对许多嵌入式控制应用提供一定高度灵活和成本低的解决办法。

AT89C2051提供以下标准功能:2K字节闪速存储器,128字节RAM,15根I/O口,两个16位定时器,一个五向量两级中断结构,一个全双工串行口,一个精密模拟比较器以及两种可选 的软件节电工作方式。空闲方停止CPU工作但允许RAM、定时器/计数器、串行工作口和中断系统继续工作。掉电方式保存RAM内容但振荡器停止工作并禁止有其它部件的工作到下一个硬件复位。

程序保密

AT89C2051设计有2个程序保密位,保密位1被编程之后,程序存储器不能再被编程除非做一次擦除,保密位2被编程之后,程序不能被读出。

软硬件的开发

AT89C2051可以采用下面两种方法开发应用系统。

1、由于89C2051内部程序存贮器为Flash,所以修改它内部的程序十分方便快捷,只要配备一个可以编程89C2051的编程器即可。调试人员可以采用程序编辑-编译-固化-插到电路板中试验这样反复循环的方法,对于熟练的MCS-51程序员来说,这种调试方法并不十分困难。但是做这种调试不能够了解片内RAM的内容和程序的走向等有关信息。

2、将普通8031/80C31仿真器的仿真插头中P1.0~P1.7和P3.0~P3.6引出来仿真2051,这种方法可以运用单步、断点的调试方法,但是仿真不够真实,比如,2051的内部模拟比较器功能,P1口、P3口的增强下拉能力等等。

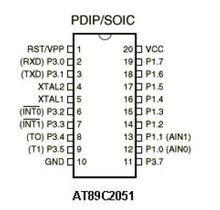

引脚说明

AT89C2051芯片引脚图

1、VCC:电源电压。

2、GND:地。

3、P1口:P1口是一个8位双向I/O口。口引脚P1.2~P1.7提供内部上拉电阻,P1.0和P1.1要求外部上拉电阻。P1.0和P1.1还分别作为片内精密模拟比较器的同相输入(ANI0)和反相输入(AIN1)。P1口输出缓冲器可吸收20mA电流并能直接驱动LED显示。当P1口引脚写入“1”时,其可用作输入端,当引脚P1.2~P1.7用作输入并被外部拉低时,它们将因内部的写入“1”时,其可用作输入端。当引脚P1.2~P1.7用作输入并被外部拉低时,它们将因内部的上拉电阻而流出电流。

4、P3口:P3口的P3.0~P3.5、P3.7是带有内部上拉电阻 的七个双向I/O口引脚。P3.6用于固定输入片内比较器的输出信号并且它作为一通用I/O引脚而不可访问。P3口缓冲器可吸收20mA电流。当P3口写入“1”时,它们被内部上拉电阻拉高并可用作输入端。用作输入时,被外部拉低的P3口脚将用上拉电阻而流出电流。

P3口还用于实现AT89C2051的各种第二功能,如下:

P3.0

RXD串行输入端口

P3.1

TXD串行输出端口

P3.2

INT0 外中断0

P3.3

INT1 外中断1

P3.4

T0定时器0外部输入

P3.5

T1定时器1外部输入

P3口还接收一些用于闪速存储器编程和程序校验的控制信号。

5、RST:复位输入。RST一旦变成高电平所有的I/O引脚就复位到“1”。当振荡器正在运行时,持续给出RST引脚两个机器周期的高电平便可完成复位。每一个机器周期需12个振荡器或时钟周期。

6、XTAL1:作为振荡器反相器的输入和内部时钟发生器的输入。

7、XTAL2:作为振荡器反相放大器的输出。

主要性能

1、和MCS-51产品兼容;

2、2KB可重编程FLASH存储器(10000次);

3、2.7-6V电压范围;

4、全静态工作:0Hz-24MHz;

5、2级程序存储器保密锁定;

6、128*8位内部RAM;

7、15条可编程I/O线;

8、两个16位定时器/计数器;

9、6个中断源;

10、可编程串行通道;

11、高精度电压比较器(P1.0,P1.1,P3.6);

12、直接驱动LED的输出端口。